Noch'ne Geschindigkeitserhöhung

Helmut BernhardtIn den letzten Jahren wurden verschiedene Möglichkeiten für Hardwarepatches zur Geschwindigkeitserhöhung bei TRS80 und GENIE vorgestellt. Allen Vorschlägen gemeinsam war, daß dies bis maximal 3,55 MHz (100% Speedup) möglich war. Voraussetzung war natürlich auch, daß 64K RAM auf dem CPU-Board vorhanden waren und daß ein Z80-A eingesetzt wird. Unterschiedlich war allerdings der Aufwand, der dafür getrieben wurde. Ein ehemaliges Mitglied war sogar der Meinung, daß der Erwerb eines Platinenschnippels mit 5 Allerwelt-ICs für den Gegenwert von 30 großen Bieren ein big Deal war, andere begnügten sich mit einfachem Umverdrahten am Frequenzteiler.

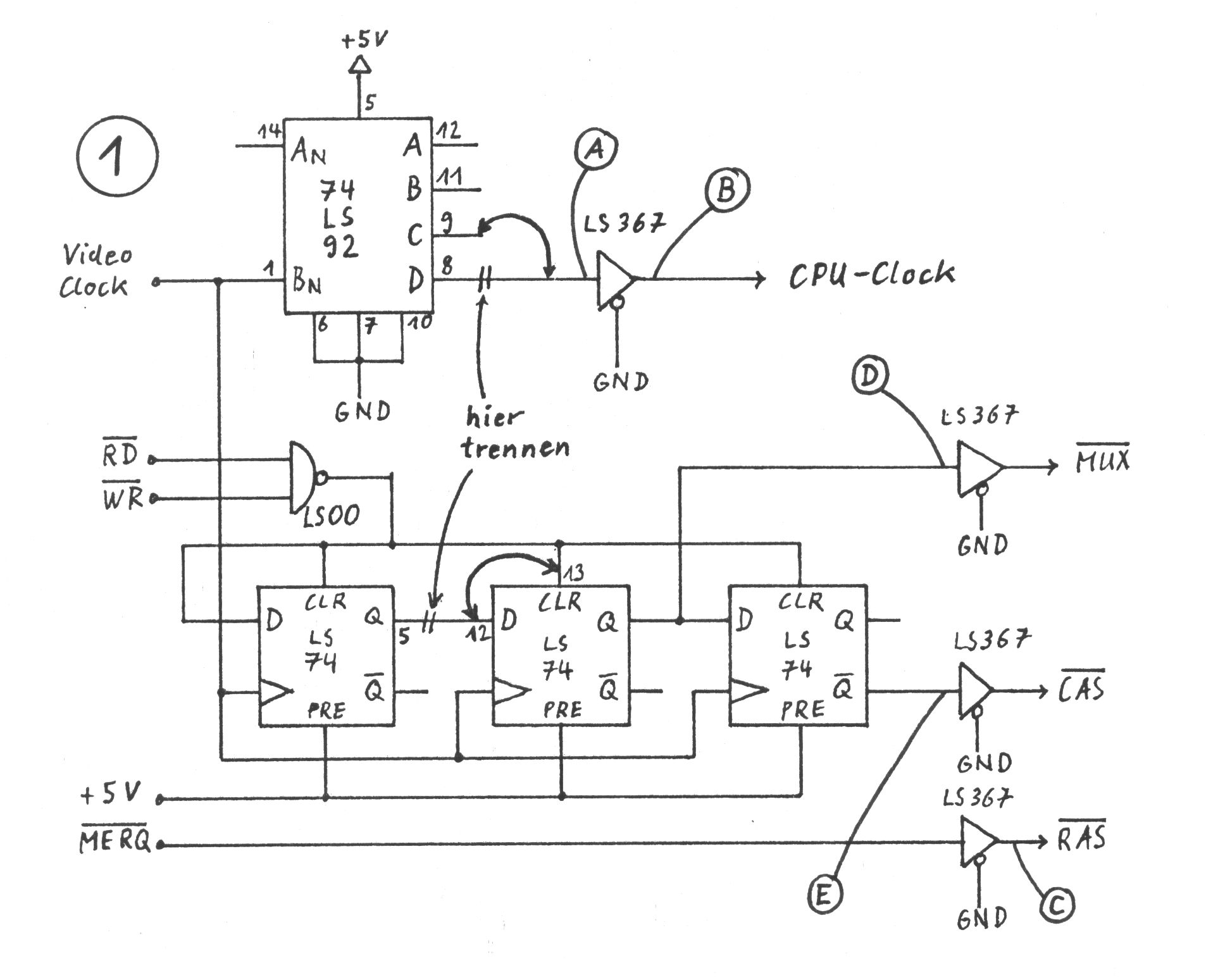

Wie auch immer vorgegangen wurde, bei 3,55 MHz war Schluß. Wenn man diese Grenze überwinden will, muß man vom vorgegebenen Prinzip der Erzeugung der RAM-Steuersignale RAS*, MUX* und CAS* aus dem Systemmuttertakt, der in seinem Wert wegen der Verwendung beim Video-Timing festgelegt ist, abrücken. Dieses Prinzip erzeugt aus dem Muttertakt und den Z80-Signalen RD* und WR* diese Signale über zwei Flip Flops. Wenn man aber am Frequenzteiler für den Z80 einen nicht so weit heruntergeteilten Takt abgreift und nicht gleichzeitig das Timing der RAM-Steuersignale ändert, läuft irgendwann beides nicht mehr synchron. Das Prinzip, wie beim TRS80 und GENIE diese Schaltungen aussehen und wie dort zur Geswindigkeitserhöhung eingegiffen werden kann, ist in Abb. 1 zu sehen.

Abb. 1: Erzeugung der Signale RAS*, MUX* und CAS*

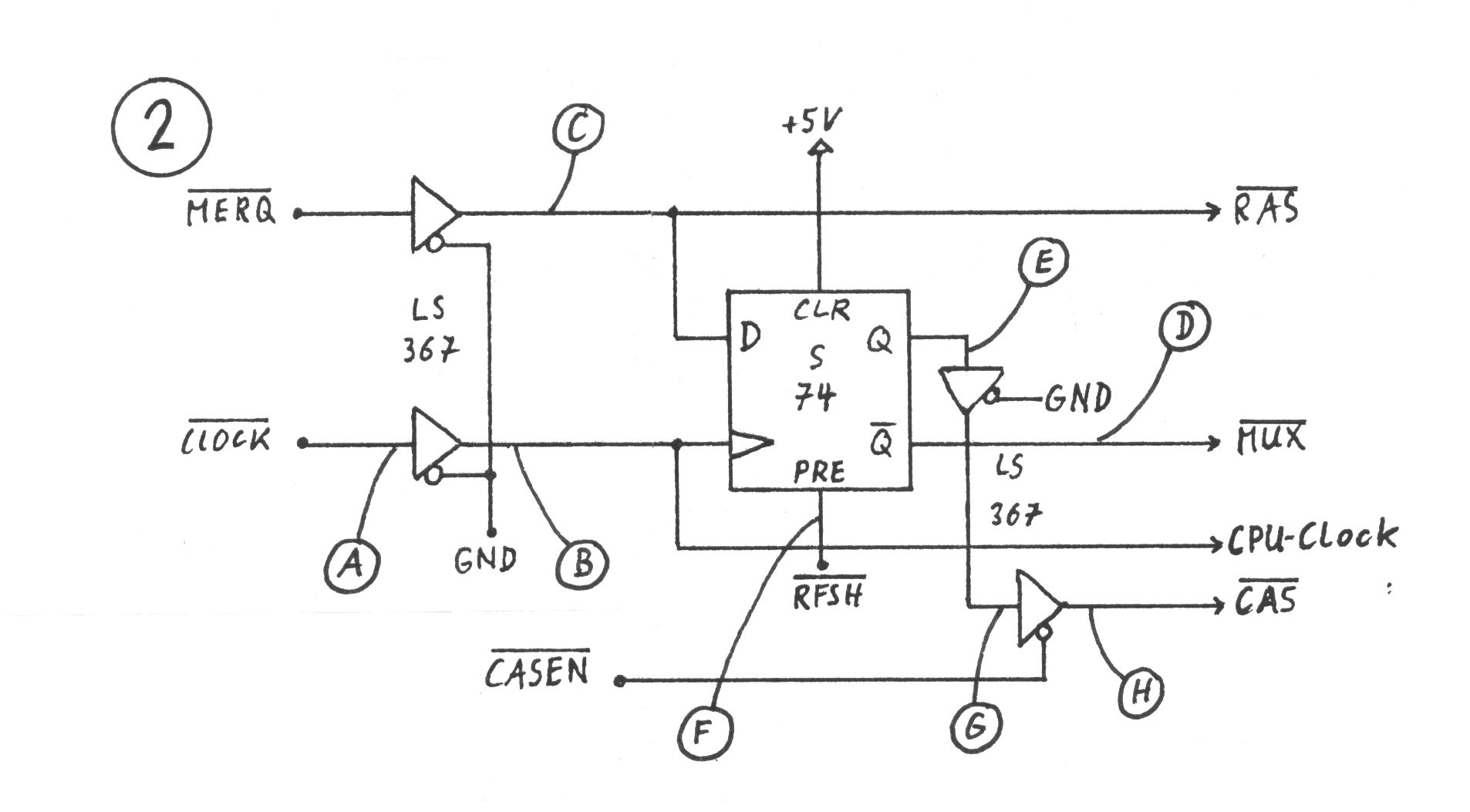

Eine andere Art der Erzeugung der Signale RAS*, MUX* und CAS* hat uns TCS im GENIE IIs vorgeführt. Dort ist eine soft- (und/oder) hardgesteuerte Umschaltung zwischen 1,77 und 5,3 (6,0 oder 8,0) MHz möglich. Dafür konnte bei so stark voneinander abweichenden Geschwindigkeiten natürlich nicht mehr ein konstantes Timing der RAM-Steuersignale verwendet werden. Die RAM-Steuersignale werden dort aus dem jeweils eingestellten CPU-Tatkt und dem Z80-Signal MERQ* hergeleitet. Wegen der dabei möglichen hohen Geschwindigkeiten wird dafür ein 74S74 Flip Flop eingesetzt.

Abb. 2: und so im TRS80 oder GENIE I oder II

Diese Variante läßt sich natürlich auch im TRS80 oder GENIE I oder II verwenden (Abb. 2). Da hierbei sowohl CPU-Takt als auch Steuerung der RAMs aus dem gleichen Takt abgeleitet werden, kann dieser beliebig gewählt werden (solange die Hardware mitspielt). Ein solcher Takt kann entweder am Teiler 74LS92 auf dem CPU-Board abgegriffen werden oder über eine einfache Oszillator-Schaltung zusätzlich erzeugt werden.

Außer den bekannten Problemen mit RAMs im Expansions-Interface und einer flinken Variante der Z80-CPU spielt irgendwann auch die Zugriffszeit der ROMs eine Rolle. In beiden Computern stecken Exemplare, deren Zugriffszeiten so ungünstig wie nur möglich sind. Es gibt aber heute schon 32K-EPROMs (27256) mit 150ns Zugriffszeit und 16K-EPROMs (27128) mit 170ns Zugriffszeit. Wenn man sich den ROM-Inhalt in ein solches IC umfüllt, sollten bedeutend höhere Taktraten möglich sein. Bei Verwendung eines 27256-EPROMs ist durch Umschalten des Pegels am Adreßeingang A14 auch ein Wechsel zwi- sch Original Level 2 und einer aufgebohrten eigenen Schöpfung möglich.

Da diese EPROMS mit ihren 28 Pins aber nicht mehr in einen der bestehenden Sockel passen und beim TRS80 auch nicht pinkompatibel zu den dort verwendeten ROMs sind, müssen ein paar Leitungen durch die Luft dorthin verdrahtet werden. Außerdem müssen die Freigabe-Signale der bisherigen ROMs über AND-Verknüpfungen zu einem gemeinsamen Freigabe-Signal für das neue EPROM zusammengefaßt werden.

Beim Umändern auf die in Abb.2 dargestellte Variante braucht nur das 74S74 Flip Flop zusätzlich eingesetzt zu werden. Die Treiber aller Signale sind auch im ursprüglichen Zustand schon vorhanden und können weiterhin benutzt werden. Die folgende Tabelle gibt für TRS80 und GENIE I und -II die Punkte an, wo das zusätzliche Flip Flop anzuschließen ist.

| Punkt | 74S74 | Signal | TRS80 | GENIE I/II | Pin | IC | Typ | Pin | IC | Typ | Pin | A | - | Clock | 37 | 367 | 2 | #1 | 72 | 367 | 12 | #1 | B | 3 | CPU-Clk | 37 | 367 | 3 | 72 | 367 | 11 | C | 2 | RAS* | 16 | 367 | 5 | 72 | 367 | 5 | D | 6 | MUX* | 37 | 367 | 4 | #2 | 72 | 367 | 2 | #2 | E | 5 | PCAS* | 37 | 367 | 14 | #2 | 72 | 367 | 10 | #2 | F | 4 | RFSH* | 16 | 367 | 3 | 40 | Z80 | 28 |

| #1 | hier kann entweder ein externer Oszillator oder eine aus dem Muttertakt über den 74LS92 heruntergeteilte Frequenz angelegt werden |

| #2 | die bisher zu diesem Pin führende Leitung wird durchtrennt |

Zum Einsatz einer HD64180-CPU ist es nur noch ein kleiner Schritt. Im Unterschied zum Z80 wird der HD64180 an den Pins 2 und 3 direkt mit einem Quartz beschaltet, der die doppelte Frequenz des beabsichtigten Systemtaktes liefert. Der HD64180 halbiert diese Frequenz intern und gibt dann diesen Systemtakt über Pin 64 aus. Systemtakt kann dann über Pin 6 der Z80-Fassung dem Computer zugefürt werden. Dabei muß natürlich die Verbindung zwischen Treiber und Pin 6 der Z80-Fassung durchtrennt werden, damit nicht alter und neuer Takt gegeneinander arbeiten. Der neue Takt braucht nur noch an das 74S74 Flip Flop und - soweit vorgesehen - auf den externen Systembus geführt zu werden.

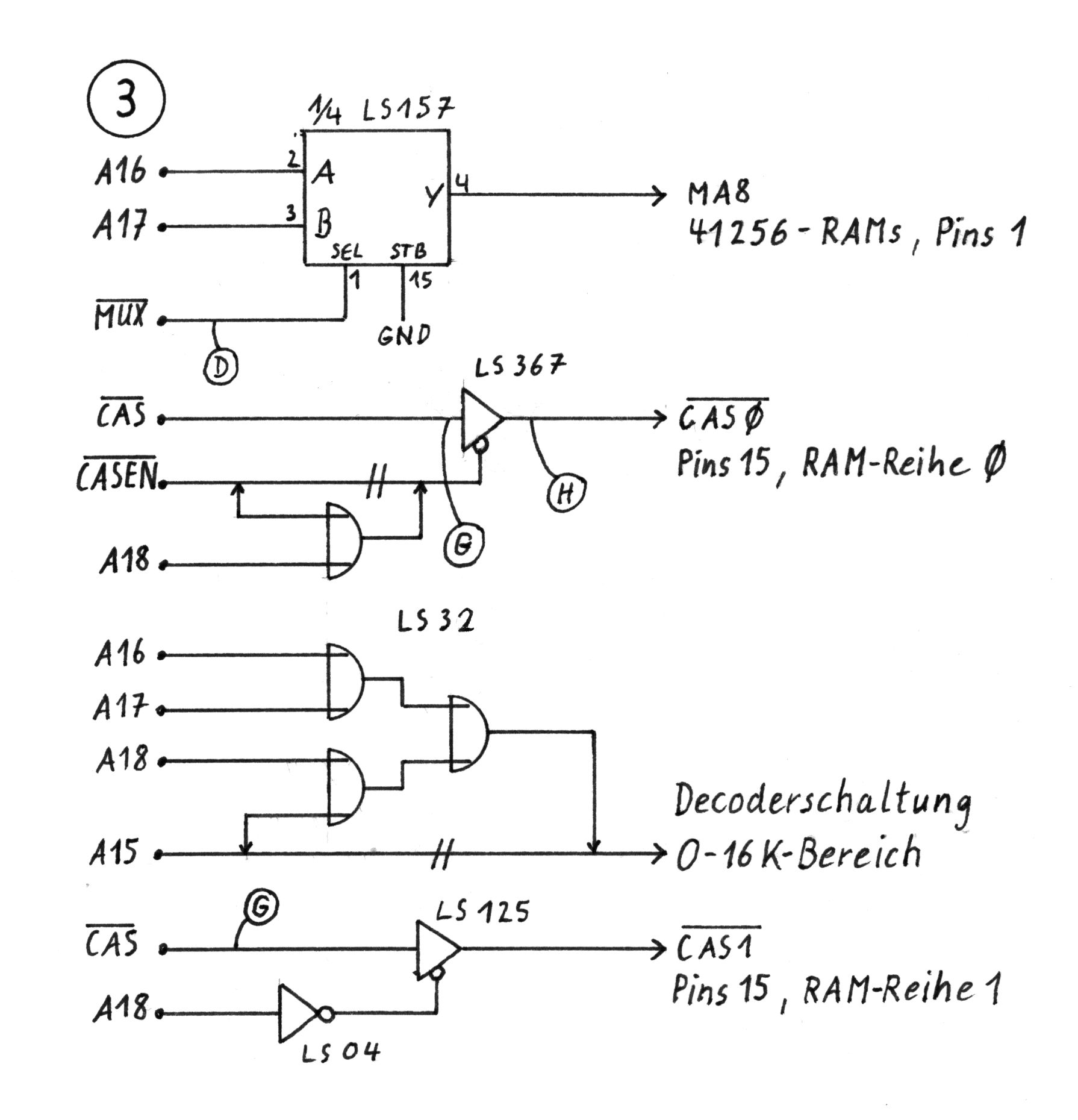

Abb. 3: Anpassung für den HD64180

Abb. 3: Anpassung für den HD64180

Im Zusammenhang mit dem HD64180 läßt sich natürlich auch noch der Speicher auf 256K oder 512K RAM erweitern. Die dabei anfallenden Änderungen gehören aber nicht mehr zum Thema und werden nur anhand von Abb. 3 kurz skizziert.

Obige Überlegungen sind für mich bislang nur Theorie. Für mich besteht im Moment nicht die Dringlichkeit, das in die Tat umzusetzen und andere Dinge dadurch zu verschieben. Ich kann also keinen Erfolg bei diesen Umbauten garantieren und auch nicht sagen, welcher Computer sich wie weit scheuchen läßt.

Vielleit ist ja irgendjemand von euch etwas mutiger und sieht dem Projekt auch einen höheren Stellenwert ab. Es würde mich freuen, wenn dieser Denkanstoß irgendwo eine Hilfe sein kann. Die beschriebenen Maßnahmen sind aber auch Vorausetzung, um in diesen Computern einen HD64180 fahren zu können und deshalb auch für mich wieder interessant (worin die Ursache dieses Beitrags liegt).